Electrical Engineering

Sneaky losses solved for resistive memory

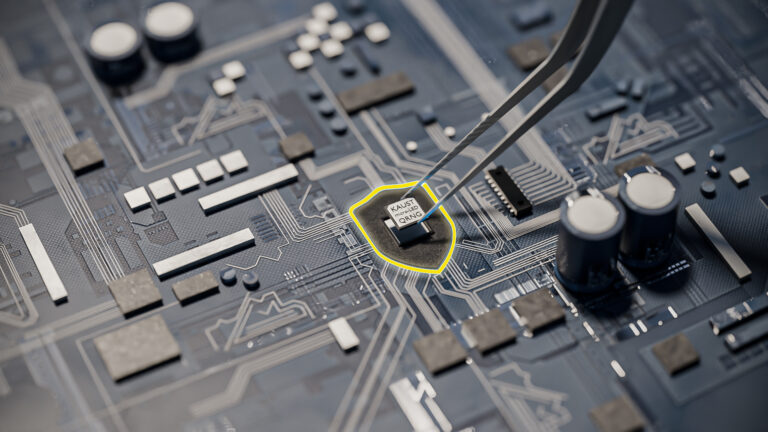

A data readout scheme achieves an unprecedented reduction in power consumption for a promising high-performance resistive memory architecture.

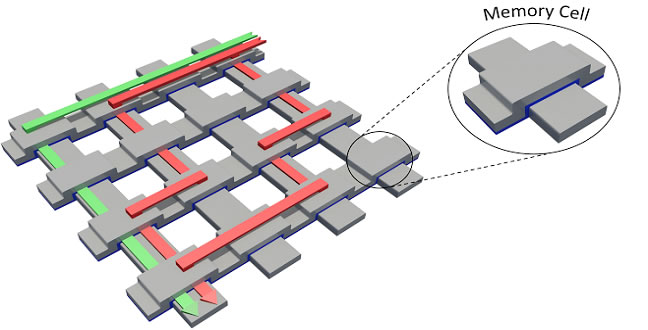

Resistive memory consists of intersecting nano-scale crossbars, where each intersection acts as a data bit with high or low resistance. When writing or reading bits, current can travel through unintended “sneak” paths, which affects reading accuracy and power consumption.

Reproduced with permission from reference 1© 2016

Resistive memory holds promise as an alternative memory architecture due to its high data density and high speed. However, even state-of-the-art “memristor” technologies are not sufficiently reliable and consume large amounts of power.

Khaled Salama and colleagues from KAUST have developed a memory reading scheme that negates the “sneaky” parasitic power losses responsible for this high power draw1.

As the memory technologies used in modern computers approach their physical limits, further gains in performance are becoming increasingly difficult to achieve.

“Existing memory technologies such as SRAM and flash memory cannot achieve high speed and high data density at the same time,” explained Salama. “Memristor memories are about to change that, with both high speed and high density as well as lower fabrication cost.”

The memristor’s superiority comes from its simplicity. Essentially, it consists of a mesh of nanoscale interconnected wires called crossbars, where each intersection acts as a data bit by switching the resistance of the intersection high or low. The bits are then written and read by applying a current to the crossbars.

“While the simplicity of the structure is its principal advantage for fabrication and performance,” said Salama, “it is also the source of its main problem—that of sneak paths—which cause inaccurate, slow and energy-hungry data access.”

When writing or reading a bit, current should only flow through the desired intersection, but, due to the simple structure, there is nothing in the crossbar to prevent current from “sneaking” through other intersections in the array. The problem is that sneak paths are different for every memory bit and even variable when reading the same bit, meaning that many successive read operations are needed to reliably read each bit. Not only is this slow, but it also results in excessively high power consumption.

Salama and his colleagues took advantage of the typical patterns of data storage in computer memory to refine how each bit is read. By estimating correlations between sneak paths on adjacent bits, they were able to achieve 100 percent readout accuracy with just a single read operation per bit with a more than ten-fold reduction in power consumption.

“Our new sneak-path-immune readout technique also requires minimal additional hardware to distinguish between memory data values,” said Salama. “This memristor technology is a promising candidate to replace hard disk drives as well as volatile and flash memories, and it is also the perfect candidate for neural bio-inspired computing.”

References

- Zidan, M.A., Omran, H., Naous, N., Fahmy, H.A.H., Lu, W.D. & Salama, K.N. Single-readout high-density memristor crossbar. Scientific Reports 6, 18863 (2016).| article

You might also like

Electrical Engineering

Gallium oxide electronics withstand extreme cold

Computer Science

AI-based hydrogen plant models improve power grid stability

Electrical Engineering

Quantum dot lasers outshine expectations

Bioengineering

Self-aware biosensors boost digital health monitoring

Bioengineering

Smart patch detects allergies before symptoms strike

Computer Science

Green quantum computing takes to the skies

Electrical Engineering

Micro-LEDs boost random number generation

Bioengineering